Zedboard Jtag Driver

Thought I would share my experience working with Zedboard (Rev C) JTAG connectivity issues with the 2014.4 SDK 1. Installed Digilent Adept drivers and utilities for both Linux and Windows: Notes on Zedboard 2014.4 SDK JTAG connectivity Zedboard.

- Dec 27, 2018 After doing this I connected the cable and Windows loaded two drivers for it: a Jungo driver and a “Xilinx USB Cable” driver under the “Programming cables” section. My Windows 10 installation of Vivado 2018.1 is now able to recognize the XUP JTAG cable and find the Zynq 7020 that’s on the Zed board.

- USB-JTAG drivers with ISE14.6/Windows764bit/Zedboard I am working with the Zedboard, ISE 14.6 and Windows7 64 bit. So far I was able to get the UART-USB driver installed working to command LED's on/off but I cannot seem to get the USB-JTAG to work.

- Download Here. The Digilent Plug-in for Xilinx ® tools allows Xilinx software tools to directly use the Digilent USB-JTAG FPGA configuration circuitry. Xilinx iMPACT™, ChipScope™ Pro, EDK Xilinx Microprocessor Debugger (XMD) command line mode, and EDK Software Development Kit (SDK) are supported by the Plug-in. Refer to www.xilinx.com for more information about these Xilinx design tools.

- Download Here. The Digilent Plug-in for Xilinx ® tools allows Xilinx software tools to directly use the Digilent USB-JTAG FPGA configuration circuitry. Xilinx iMPACT™, ChipScope™ Pro, EDK Xilinx Microprocessor Debugger (XMD) command line mode, and EDK Software Development Kit (SDK) are supported by the Plug-in. Refer to www.xilinx.com for more information about these Xilinx design tools.

- ARM Processor Not Detecting in Hardware Manager Hello when i am trying to load the program through USB Jtag (micro USB Connector) i am seeing only ZC7020 but not the ARM Processor in the scan chain. I am using Zedboard.

- Linux version running on a host development system (where the USB JTAG cable driver would be running) Linux running on a target (e.g. Zynq 7000) device These are entirely different and separate sets of contexts, needs, and requirements.

You must install the Altera® USB-BlasterTM or Altera USB-Blaster IIdownload cable driver before you can use it to program devices with Quartus® Prime software.

The first time the USB-Blaster download cable is plugged in, the Windows Found New Hardware dialog box prompts you to install the driver. (Note: Do not use the Add HardwareWizard from the Control Panel.)

The USB-Blaster II device drivers require manual installation so that the cable will be properly recognized. Refer to the instructions below.

The Altera On-Board USB-Blaster II cable appears as Altera USB-Blaster (unconfigured) when first attached to your system. After it has been configured by the Quartus Prime software, it will appear as Altera USB-Blaster II (JTAG interface) and then Altera USB-Blaster II (SystemConsole interface). You might need to install drivers for each of these interfaces; follow the steps below to install the drivers.

You must have system administration (Administrator) privileges to install the USB-Blaster and USB-Blaster II download cable driver.

Driver Installation for Altera USB-Blaster

- Plug the USB-Blaster download cable into your PC. The Found New Hardware dialog box appears.

- Select Locate and install driver software (recommended).

- Select Don't search online.

- When you are prompted to Insert the disc that came with your USB-Blaster, select I don’t have the disc. Show me other options.

- Select Browse my computer for driver software (advanced) when you see the Windows couldn’t find driver software for your device dialog box.

- Click Browse, and browse to the<Path to Quartus Prime installation>driversusb-blaster directory.

- Note: Do not select the x32 or x64 directories.

- Click OK.

- Select the Include subfolders option, and click Next.

- If you are prompted Windows can’t verify the publisher of this driver software, select Install this driver software anyway in the Window Security dialog box. The installation wizard guides you through the installation process.

- When The software for this device has been successfully installed dialog box appears, click Close.

- To complete your installation, set up programming hardware in the Quartus Prime software.

Driver Installation for Altera USB-Blaster II

- Plug the USB-Blaster II cable into your PC.

- Open the Device Manager, and right-click on the Unknown device under the Other devices branch.

- Select Update Driver Software.

- Select Browse my computer for driver software.

- Enter the location of the Quartus Prime software USB-Blaster II driver files directory (<Path to Quartus Prime installation>driversusb-blaster-ii) in the Search for driver software in this location field.

- Click Next.

- Click Install in the Would you like to install this device software? Windows security dialog box.

- Close the Update Driver Software - Altera USB-Blaster II (Unconfigured) successful installation notification. The Device Manager now shows a new branch called JTAG cables with an Altera USB-Blaster II (Unconfigured) node.

- Open the Quartus Prime Programmer. Within a few seconds, the JTAG cables branch displays two nodes: Altera USB-Blaster II (JTAG interface) and Altera-USB Blaster II (System Console interface).

Overview

ZedBoard specs (Rev D):

- Xilinx Zynq-7000 AP SoC XC7Z020-CLG484-1

- Programmable logic:

- Derived from Xilinx Artix-7 FPGA

- Includes configurable logic blocks (CLBs), port and width configurable block RAM (BRAM), DSP slices with a 25 x 18 multiplier, 48-bit accumulator and pre-adder (DSP48E1), a user configurable analog to digital convertor (XADC), clock management tiles (CMT), etc

- Dual-core ARM Cortex A9

- ARMv7-A architecture, r3p0 revision

- 667 MHz max clock frequency (speed grade -1)

- L1 cache: 32 KB instruction, 32 KB data per processor

- L2 cache: 512 KB

- 256KB on chip memory (OCM)

- Memory:

- 512 MB DDR3 SD RAM (32-bit address)

- 256 Mb QSPI flash memory

- Static memory controller

- 4 GB SD card

- Onboard USB-JTAG Programming

- 10/100/1000 Ethernet

- USB OTG 2.0 and USB-UART

- PS & PL I/O expansion (FMC, Pmod™, XADC)

- GPIO with four 32-bit banks, of which up to 54 bits can be used with the PS I/O and up to 64 bits connected to the PL

- Up to 54 flexible multiplexed I/O (MIO) for peripheral pin assignments

- Multiple displays (1080p HDMI, 8-bit VGA, 128 x 32 OLED)

- I2S Audio CODEC

- See http://www.digilentinc.com/zedboard

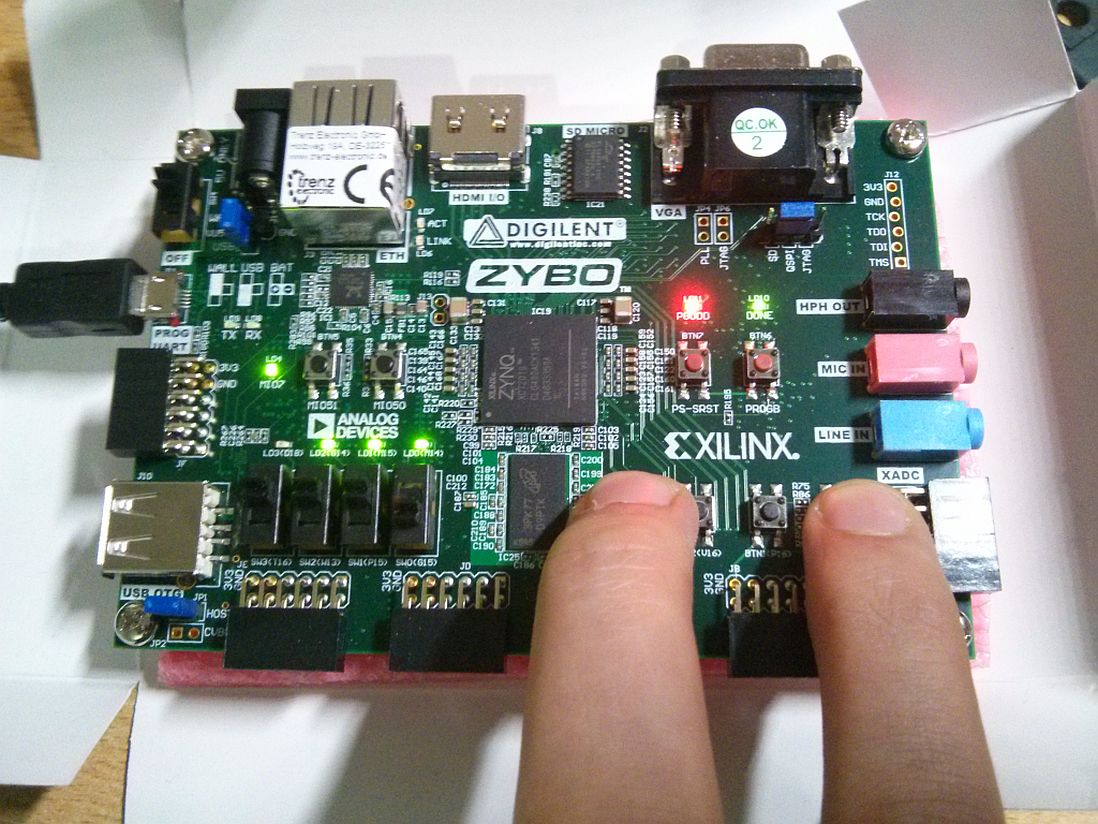

ZedBoard images

(from http://zedboard.org/product/zedboard)

| Front | Back |

|---|---|

| Functional Overlay | Block Diagram |

- Zynq-7000 AP SoC overview

(from http://www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf)

Zedboard Jtag Driver Windows 10

Host OS:

- Ubuntu Linux 14.04.3 LTS (GNU/Linux 3.16.0-50-generic x86_64)

- See http://releases.ubuntu.com/14.04/

- Ubuntu Linux 14.04.3 LTS (GNU/Linux 3.16.0-50-generic x86_64)

Xilinx applications:

- Vivado Design Suite (including SDK) 2015.2

- See http://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/2015-2.html

- PetaLinux 2015.2

- See http://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/embedded-design-tools/2015-2.html

- Vivado Design Suite (including SDK) 2015.2

Installation

- Install Xilinx applications:

- Install necessary packages from official Ubuntu repository:

- Install cable drivers:

- Change /bin/sh to bash

- Install serial terminal console:

Setup TFTP server

- Create a text file /etc/xinetd.d/tftp with the following content:

- Create a directory /tftpboot

- Restart the xinetd service

Setup DHCP server

- Set a network connection profile with

- Install DHCP server

- Edit /etc/dhcp/dhcpd.conf and /etc/default/isc-dhcp-server according to https://help.ubuntu.com/lts/serverguide/dhcp.html

- e.g.

- Restart

Setup NFS server

- Install NFS server

- Edit /etc/exports according to https://help.ubuntu.com/community/SettingUpNFSHowTo#Install_NFS_Server

- e.g.

- Restart

- Note that if you have firewall running, you have to keep the port 2049 open (or disable the firewall).

Startup

- Get a license from http://www.xilinx.com/getlicense

- Use the voucher to get a node-locked license (which will be emailed to you)

- Alternatively, one can get the WebPACK license for free

- In Vivado, select Help -> Manage License.., load the license Xilinx.lic

- Setup the environments:

Useful info

References

- ZedBoard Hardware User's Guide

http://zedboard.org/sites/default/files/documentations/ZedBoard_HW_UG_v2_2.pdf - ZedBoard Master Constraints

http://zedboard.org/sites/default/files/documentations/zedboard_master_XDC_RevC_D_v2.zip - Zynq-7000 Technical Reference Manual (UG585)

http://www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf - Zynq-7000 All Programmable SoC Overview (DS190)

http://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf - ARM Cortex-A9 Technical Reference Manual

http://infocenter.arm.com/help/topic/com.arm.doc.ddi0388g/DDI0388G_cortex_a9_r3p0_trm.pdf

- ZedBoard Hardware User's Guide

Zynq-7000 IP (ZYNQ7 Processing System) in Vivado 2015.2 with ZedBoard preset

- Zynq-7000 memory map/address map

(from http://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf)- Each unique 32-bit address holds one byte.

Zynq-7000 clocks

- Generated by three programmable PLLs: ARM PLL, DDR PLL, I/O PLL

- (Default) Input frequency: 33.333333 MHz, CPU clock ratio 6:2:1

- CPU freq: 667 MHz, DDR freq: 533 MHz

Zynq-7000 APU

- Dual-core ARM Cortex-A9 processor

- ARMv7 architecture, runs 32-bit ARM instructions, 16-bit and 32-bit Thumb instructions, 8-bit Java byte codes, implements ARM NEON coprocessor technology, a single instruction multiple data (SIMD) architecture

- Snoop control unit (SCU)

- L2 cache controller

- On-chip memory (OCM)

- 8-channel DMA

- System watchdog timer

- Triple-timer controller (TTC)

- Dual-core ARM Cortex-A9 processor

Zynq-7000 PS-PL interface

- 2x 32-bit AXI general-purpose (GP) master interfaces

- 2x 32-bit AXI general-purpose (GP) slave interfaces

- 4x 64-bit AXI high-performance (HP) slave interfaces

- 1x 64-bit AXI Accelerator Coherency Port (ACP) slave interface

- 4x PS clock outputs to PL

- 4x PS reset outputs to PL

- 16x interrupts

- DMA, event signals, EMIO, ..

Zynq-7000 interrupts

- 64 shared peripheral interrupts (PL interrupts + PS IOP interrupts) are supported, starting from ID 32

ZedBoard schematics

http://zedboard.org/sites/default/files/documentations/ZedBoard_RevD.2_Schematic_130516.pdfZedBoard Out Of Box (OOB) SD card image and source can be downloaded from Digilent website: http://www.digilentinc.com/Data/Products/ZEDBOARD/ZedBoard_OOB_Design.zip

- A backup copy of the OOB SD card can be found in the 'bootimage' directory

PetaLinux Tools

- See http://www.xilinx.com/tools/petalinux-sdk.htm

- Also see http://www.wiki.xilinx.com/PetaLinux

- PetaLinux v2015.2.1 is based on Yocto 1.8, which is based on Linux 3.19

- PetaLinux v2015.2.1 includes BusyBox 1.23.1 and Dropbear SSH server

- The git trees for PetaLinux v2015.2.1 are (according to http://www.xilinx.com/support/answers/65276.html):

- https://github.com/Xilinx/linux-xlnx (tag: xilinx-v2015.2.03)

- https://github.com/Xilinx/u-boot-xlnx (tag: xilinx-v2015.2)

- https://github.com/Xilinx/device-tree-xlnx.git (tag: xilinx-v2015.2.02)

- The git trees for PetaLinux v2015.4 are (according to http://www.xilinx.com/support/answers/66107.html):

- https://github.com/Xilinx/linux-xlnx (tag: xilinx-v2015.4)

- https://github.com/Xilinx/u-boot-xlnx (tag: xilinx-v2015.4)

- https://github.com/Xilinx/device-tree-xlnx.git (tag: xilinx-v2015.2.4)

- Xilinx Wiki for Linux tools

PetaLinux Workflow

cd <PetaLinux_Project>petalinux-create -t project -n software --template zynqcd <Vivado_Export_to_SDK_Directory>petalinux-config --get-hw-description -p <PetaLinux_Project>/software/- Make sure that 'primary sd' is selected in

- Subsystem AUTO Hardware Settings > Advanced bootable images storage Settings > boot image settings > image storage media

- Subsystem AUTO Hardware Settings > Advanced bootable images storage Settings > kernel image settings > image storage media

- (Optional)

petalinux-config -c rootfs - (Optional)

petalinux-config -c kernel

- Make sure that 'primary sd' is selected in

petalinux-create -t apps -n myapp --template c --enablepetalinux-build- Make necessary changes to device tree settings found in subsystems/linux/configs/device-tree/

cd images/linuxpetalinux-package --boot --fsbl zynq_fsbl.elf --fpga system_wrapper.bit --uboot- Copy BOOT.BIN and image.ub (roughly 11 MB) to the SD card.

- The SD card has to be formatted as FAT32.

- Boot the ZedBoard with the SD card (make sure the jumpers are set correctly).

- Copy BOOT.BIN and image.ub (roughly 11 MB) to the SD card.

PetaLinux netboot using TFTP

- Use SD card for initial boot. Connect the ethernet cable.

- When the message 'Hit any key to stop autoboot' shows, stop the autoboot.

- If an IP address was not obtained, run

dhcp. - Run

set serverip 192.168.1.1(TFTP server IP). - Run

run netboot.

AXI reference guide

Acronyms

| Acronym | Definition |

|---|---|

| ACP | Accelerator Coherency Port |

| AP SoC | All Programmable System on a Chip |

| APB | Advanced Peripheral Bus |

| APU | Application Processor Unit |

| ASIC | Application-Specific Integrated Circuit |

| AXI | Advanced eXtensible Interface |

| BSP | Board Support Package |

| CLB | Configurable Logic Block |

| DMA | Direct Memory Access |

| DRM | Direct Rendering Manager |

| DSP | Digital Signal Processor |

| DTB | Device Tree Binary |

| DTS | Device Tree Source |

| EMIO | Extended MIO |

| FIFO | First In, First Out |

| FMC | FPGA Mezzanine Card |

| FPGA | Field-Programmable Gate Array |

| FSBL | First-Stage Boot Loader |

| GDB | GNU Project Debugger |

| GIC | Generic Interrupt Controller |

| GNU | GNU's Not Unix |

| GPIO | General-Purpose I/O |

| HDL | Hardware Description Language |

| HLS | High-Level Synthesis |

| I2C | Inter-Integrated Circuit |

| IDE | Integrated Development Environment |

| IOP | Input/Output Peripherals |

| IP | Intellectual Property |

| IRQ | Interrupt ReQuest |

| JTAG | Joint Test Action Group |

| LUT | Look-Up Tables |

| LVDS | Low Voltage Differential Signal |

| MIO | Multiplexed I/O |

| MMU | Memory Management Unit |

| OCM | On-Chip Memory |

| OS | Operating System |

| PL | Programmable Logic (a.k.a. fabric) |

| PLL | Phase-Locked Loop |

| PS | Processing System (a.k.a. processor) |

| QSPI | Quad Serial Peripheral Interface |

| RTL | Register Transfer Level |

| SCU | Snoop Control Unit |

| SDK | Software Development Kit |

| SIMD | Single Instruction Multiple Data |

| SoC | System on a Chip |

| TLA | Three-Letter Acronym |

| TLB | Translation Lookaside Buffer |

| TTC | Triple-Timer Counter |

| UART | Universal Asynchronous Receiver/Transmitter |

| UIO | Userspace I/O |

Tutorials

Zedboard Jtag Driver

ZedBoard Getting Started Guide

http://zedboard.org/sites/default/files/documentations/GS-AES-Z7EV-7Z020-G-V7.pdfAvnet Zynq SpeedWay Workshops

http://zedboard.org/support/trainings-and-videos- Developing Zynq-7000 All Programmable SoC Hardware

http://zedboard.org/node/2563/ - Developing Zynq-7000 All Programmable SoC Software

http://zedboard.org/node/2540/ - PetaLinux for the Zynq-7000 All Programmable SoC

http://zedboard.org/course/petalinux-zynq%C2%AE-7000-all-programmable-soc

- Developing Zynq-7000 All Programmable SoC Hardware

Zynq Design From Scratch blog by Sven Andersson

http://svenand.blogdrive.com/Vivado Design Suite Tutorial: Embedded Processor Hardware Design (UG940)

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2015_2/ug940-vivado-tutorial-embedded-design.pdf- Remember to download the tutorial design files

Xilinx University Program Workshops

http://www.xilinx.com/support/university/workshops.html- Embedded System Design Flow on Zynq

http://www.xilinx.com/support/university/vivado/vivado-workshops/Vivado-embedded-design-flow-zynq.html - Advanced Embedded System Design on Zynq

http://www.xilinx.com/support/university/vivado/vivado-workshops/Vivado-adv-embedded-design-zynq.html - Embedded Linux on Zynq

http://www.xilinx.com/support/university/vivado/vivado-workshops/Vivado-embedded-linux-zynq.html

- Embedded System Design Flow on Zynq

Zynq-7000 All Programmable SoC: Embedded Design Tutorial (UG1165)

http://www.xilinx.com/support/documentation/sw_manuals/xilinx2015_2/ug1165-zynq-embedded-design-tutorial.pdf- Remember to download the tutorial design files

Zynq Base Targeted Reference Design (TRD) 2015.2

http://www.xilinx.com/support/documentation/boards_and_kits/zc702_zvik/2015_2/ug925-zynq-zc702-base-trd.pdf

http://www.wiki.xilinx.com/Zynq+Base+TRD+2015.2⚠️ For ZC702 Evaluation Board, not ZedBoard!- Remember to download the tutorial design files

Reading materials

- The Zynq Book

http://www.zynqbook.com/ - Xilinx UltraFast Embedded Design Methodology Guide (UG1046)

http://www.xilinx.com/support/documentation/sw_manuals/ug1046-ultrafast-design-methodology-guide.pdf

- The Zynq Book

Known Issues (PetaLinux)

Release Notes and Known Issues for PetaLinux 2013.04 and later (AR# 55776)

Ethernet

- Insert the following into subsystems/linux/configs/device-tree/system-top.dts

- See http://www.xilinx.com/support/answers/61117.html

- Insert the following into subsystems/linux/configs/device-tree/system-top.dts

UIO

- Replace

compatiblefor each GPIO device in subsystems/linux/configs/device-tree/pl.dtsi

- Replace

bootargsin subsystems/linux/configs/device-tree/system-conf.dtsi- See https://github.com/Xilinx/linux-xlnx/commit/7ebd62dbc727ef343b07c01c852a15fc4d9cc9e5 for explanation.

- Replace

Miscellaneous (PetaLinux)

Enable TCF agent

Enable SSH server

Stitch-and-glue construction, along with the development of epoxy and modern mahogany marine plywood, has revolutionized and revitalized wooden boat building. This method of building is not only stronger, lighter, and faster than traditional wooden boat building, but it also takes far less skill. Free Stitch and Glue Boat Plans in no Particular Order. Apple Pie Pram I built this and found it to be a lovely usable tender. Clown 450 Free sailboat plans and instructions IN FRENCH but nicely illustrated. Micro Folding Dinghy Free Plans. Since the seams are glued but not rigid. The resulting boat is incredibly light weight, strong, and durable. Plans packages for Stitch-N-Glue designs include instructions, material layouts, and material listings. In addition, the Full Size Patterns provided with all Stitch-N-Glue designs are precise since they’re taken from the actual panels used to build our prototype boats. Designs for Stitch & Glue Construction This directory includes all of the plans that are specifically designed for stitch and glue construction. The RC Model X-1 is an inexpensive way to try out this popular contruction method. Stitch and glue boat plans free pdf.

Mount via NFS

Change MAC address

Use static IP address

Run applications at startup

- See AR# 55998

- Create an application, and create a startup script in the application area

- Modify the Makefile, remove any reference to

APP_OBJSand*.o, update theinstallsection to copymystartupto/etc/init.d/and create a symbolic link to/etc/rc5.d/

- Remember to indent with a tab character, otherwise the Makefile won't work

Auto login

- Add a new file

build/linux/rootfs/targetroot/bin/autologinwith the following content:

- Make

autologinexecutable

- Modify

build/linux/rootfs/targetroot/etc/inittab, change the very last line to

- Repackage the image

- Add a new file

Use an external Linux kernel

Update device tree generator